Sự khác biệt cơ bản giữa logic CMOS và TTL bao gồm các thành phần CMOS đắt hơn, các mạch CMOS không thu được nhiều điện năng và mức tiêu thụ điện năng TTL tăng chậm hơn. Các khác biệt khác bao gồm việc truyền tín hiệu kỹ thuật số và hư hỏng tính nhạy cảm.

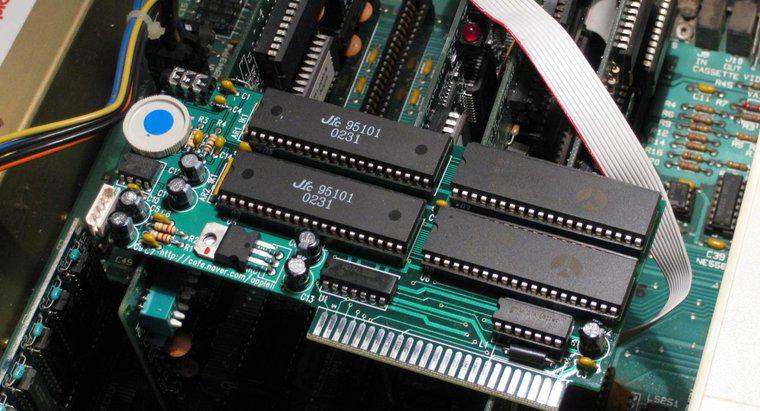

Các thành phần TTL thường ít tốn kém hơn các thành phần CMOS. Tuy nhiên, do chip nhỏ hơn, CMOS nhìn chung ít tốn kém hơn ở cấp độ hệ thống. Khi ở trạng thái nghỉ, mạch CMOS không sử dụng nhiều điện năng như mạch TTL. Tuy nhiên, tốc độ xung nhịp cao hơn khiến mức tiêu thụ điện năng của CMOS tăng với tốc độ nhanh hơn so với TTL. Các thành phần CMOS có nhiều khả năng bị hỏng do phóng tĩnh điện hơn các thành phần TTL. Tín hiệu kỹ thuật số rẻ hơn và đơn giản hơn với chip CMOS do thời gian tăng và giảm dài hơn.

Công suất tiêu tán của CMOS thường là 10 nW trên mỗi cổng trong khi mức tiêu tán công suất của TTL thường là 10 mW trên mỗi cổng. Độ trễ lan truyền của TTL thường là 10 nS trong khi độ trễ lan truyền của CMOS nói chung là từ 25 nS đến 50 nS.

Phạm vi mức điện áp cho TTL nói chung là 4,75V - 5,25V. Dải mức điện áp cho CMOS nằm trong khoảng từ 0 đến 1/3 VDD ở mức thấp và 2/3 VDD đến VDD ở mức cao.